|

NEWS

|

|

| [Jan 2024] Research paper COBRRA: COntention aware cache Bypass with Request-Response Arbitration by Aritra Bagchi et al. published in ACM TECS. |

| [Dec 2023] Research paper NeuroCool: Dynamic Thermal Management of 3D DRAM for Deep Neural Networks through Customized Prefetching by Shailja Pandey et al. published in ACM TODAES. |

| [Sep 2023] Research paper CABARRE: Request Response Arbitration for Shared Cache Management by Garima Modi et al. (Intel collaboration) presented at CODES+ISSS and published in ACM TECS. |

| [Aug 2023] Research paper Dynamic Thermal Management of 3D Memory through Rotating Low Power States and Partial Channel Closure by Lokesh Siddhu et al. accepted for publication in ACM TECS. |

| [May 2023] Research paper Performance and Energy Studies on NC-FinFET Cache-based Systems with FN-McPAT by Divya Praneetha Ravipati et al. (collaboration with Univ. of Stuttgart) accepted for publication at IEEE Transactions on VLSI Systems. |

| [Mar 2023] P. R. Panda delivers invited talk at Qualcomm Tech Talk Series |

| [Oct 2022] Best Paper Nomination at ESWEEK/ CODES+ISSS'22 for our paper NeuroMap: Efficient Task Mapping of Deep Neural Networks for Dynamic Thermal Management in High-Bandwidth Memory, by S. Pandey and P. R. Panda. Published at IEEE TCAD. |

| [Apr 2022] P. R. Panda delivers invited talk at Intel Tech Elevate Summit 2022 |

| [Apr 2022] Research paper CoMeT: An Integrated Interval Thermal Simulation Toolchain for 2D, 2.5D, and 3D Processor-Memory Systems (collaboration with Univ. of Amsterdam and Karlsruhe Inst. of Tech.) accepted for publication in ACM TACO. |

| [Mar 2022] Best Paper Nomination at DATE'22 for our paper CoreMemDTM: Integrated Processor Core and 3D Memory Dynamic Thermal Management for Improved Performance, by L. Siddhu, R. Kedia, P. R. Panda |

| [Mar 2022] Research paper FN-CACTI: Advanced CACTI for FinFET and NC-FinFET Technologies by Divya Praneetha Ravipati et al. (collaboration with Univ. of Stuttgart and Karlsruhe Inst. of Tech.) published in in IEEE Transactions on VLSI Systems. |

| [Feb 2022] P. R. Panda delivers invited talk at Google Performance Power Summit 2022 |

| [Jan 2022] P. R. Panda is the program chair of CASES'22 |

| [Jan 2022] Naman Jain wins the PMRF Fellowship to support his research collaboration with Stanford University |

| [Dec 2021] P. R. Panda and Shailja Pandey present invited talk and tutorial at NSM Winter School on Computer Architecture |

| [Dec 2021] P. R. Panda delivers invited talk at Madhya Pradesh Vigyan Sammelan, IIT Indore |

| [Oct 2021] P. R. Panda delivers invited talk at Techfest, IIT Bombay |

| [Oct 2021] P. R. Panda is the program co-chair of CASES'21 |

| [Mar 2021] P. R. Panda delivers invited talk at FDP on RISC-V VLSI Implementation Flow, IITG, MNIT, NIT-P, and IIITDM |

| [Feb 2021] Research paper Leakage-Aware Dynamic Thermal Management of 3D Memories by L. Siddhu, R. Kedia, P. R. Panda published in ACM TODAES |

| [Feb 2020] Survey paper A survey of cache simulators by H. Brais et al. published in ACM Computing Surveys |

| [Jan 2020] Ayushi Agrawal wins the PMRF Fellowship to support her research collaboration with NXP and SRC |

| [Jan 2020] P. R. Panda is appointed Editor-in-Chief of IEEE Embedded Systems Letters (ESL) journal |

| [Nov 2019] Neetu Jindal is conferred the PhD degree at IITD's 50th Convocation ceremony. She was part of the research collaboration with Freescale/NXP and SRC. Now at Intel. |

| [Oct 2019] Research paper PredictNcool: Leakage Aware Thermal Management for 3D Memories Using a Lightweight Temperature Predictor by L. Siddhu and P. R. Panda presented at CODES+ISSS'19 , New York (published in ACM TECS) |

| [Oct 2019] Research paper Alleria: An Advanced Memory Access Profiling Framework by H. Brais and P. R. Panda presented at CODES+ISSS'19 , New York (published in ACM TECS) |

| [Oct 2019] Research paper REAL: REquest Arbitration in Last Level Caches by S. Tiwari, S. Tuli, I. Ahmad, A. Agarwal, P. R. Panda, and S. Subramoney, published in ACM TECS |

| [Aug 2019] New research project Algorithms and Architectures for Machine Learning and Computing on the Edge sponsored by Cadence Design Systems initiated. |

| [Aug 2019] Book chapter Manycore processor architectures by P. Chakraborty, B. N. Swamy, and P. R. Panda published in Many-Core Computing: Hardware and Software, eds. B. M. Al-Hashimi and G. V. Merrett, IET |

| [Jul 2019] P. R. Panda delivered the keynote address at VDAT'19, Indore |

| [Feb 2019] Research paper DHOOM: Reusing Design-for-Debug Hardware for Online Monitoring by Neetu Jindal, Sandeep Chandran, et al. presented at DAC 2019 |

| [Mar 2019] Research paper "FastCool: Leakage Aware Dynamic Thermal Management of 3D Memories" by Lokesh Siddhu and P. R. Panda presented at DATE'19, Florence. |

| [Feb 2019] Research paper Enhancing Network-on-Chip Performance by Reusing Trace Buffers by Neetu Jindal,Shubhani Gupta, Divya Praneetha et al. published in IEEE Transactions on CAD. |

| [Jan 2019] Rahul Jain wins the Best PhD Thesis Award at the 32nd Intl. Conf. on VLSI Design and 18th Intl. Conf. on Embedded Systems for his thesis titled Machine Learned Machines: Reinforcement Learning Exploration for Architecture Co-optimization. The research was supported by Intel and DST/SERB's PM Fellowship program. |

| [Jan 2019] Ayushi Agrawal (with team-mates Anupam Sobti and Saurabh Tewari) wins the first prize in the Cadence Tensilica Hackathon at VLSID 2019. |

| [Jan 2019] P. R. Panda is the general co-chair of the 32nd Intl. Conf. on VLSI Design and 18th Intl. Conf. on Embedded Systems |

| [Nov 2018] Sandeep Chandran is awarded the PhD degree at the 49th Convocation. Wins the FITT Award (incl. cash prize of Rs. 60,000) for the Best Industry Relevant PhD Project in IIT Delhi. Freescale/NXP Semiconductor and Semiconductor Research Consortium were collaborators. |

| [Sep 2018] P. R. Panda is Head, Amar Nath and Shashi Khosla School of Information Technology, IIT Delhi |

| [Jul 2018] Isaar Ahmed, Aritra Bagchi, and Ayushi Agarwal join our research group. Welcome! |

| [Apr 2018] Research paper "Reusing Trace Buffers as Victim Caches" by Neetu Jindal et al. accepted for publication in IEEE Transactions on VLSI Systems. |

| [Apr 2018] Lecture video series for the online course "Synthesis of Digital Systems" available on Youtube. |

| [Jan 2018] Book chapter: P. R. Panda, "Memory Architectures" published in S. Ha and J. Teich, "Handbook of Hardware/Software Codesign", Springer, 2017. |

| [Jan 2018] P. R. Panda is an Associate Editor of IEEE Transactions on CAD |

| [Jan 2018] P. R. Panda is an Associate Editor of IEEE Transactions on Multi-Scale Computing Systems. |

| [Oct 2017] Rahul Jain defends his PhD thesis |

| [Aug 2017] Research paper "Cooperative Multi-Agent Reinforcement Learning based Co-optimization of Cores, Caches, and On-chip Network" by R. Jain, P. R. Panda, and S. Subramoney accepted for publication in ACM Transactions on Architecture and Code Optimization. |

| [Jun 2017] New Research Project on Smartphone Energy Efficiency sponsored by Samsung initiated. |

| [May 2017] New Research Project on Memory Hierarchy in Multiprocessor Systems-on-Chip sponsored by Semiconductor Research Corporation (SRC) initiated. |

| [Mar 2017] Research paper "A Coordinated Multi-Agent Reinforcement Learning Approach to Multi-Level Cache Co-partitioning" by Rahul Jain, P. R. Panda, and S. Subramoney, presented at DATE'17, Lausanne. |

| [Mar 2017] Research paper "Reusing Trace Buffers to Enhance Cache Performance" by Neetu Jindal et al., presented at DATE'17, Lausanne. |

| [Feb 2017] P. R. Panda delivered inaugural talk "Embedded Systems-on-Chip: Research at the Forefront of VLSI Systems" and seminars on Hardware Synthesis at Faculty Development Programme in MNIT Jaipur. |

| [Jan 2017] Research paper "Managing Trace Summaries to Minimize Stalls During Post-silicon Validation" by S. Chandran et al. to appear in IEEE Transactions on VLSI Systems. |

| more |

I am a Professor of Computer Science and Engineering at IIT Delhi, and Associated Faculty of the Khosla School of Information Technology. My research interests are in the areas of:

I am a Professor of Computer Science and Engineering at IIT Delhi, and Associated Faculty of the Khosla School of Information Technology. My research interests are in the areas of:

Synthesis of Digital Systems

Synthesis of Digital Systems Power-efficient System Design

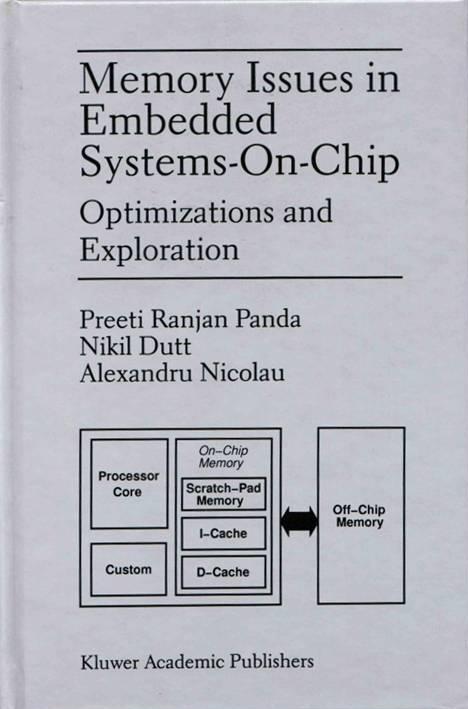

Power-efficient System Design Memory Issues in Embedded Systems-On-Chip: Optimizations and

Exploration

Memory Issues in Embedded Systems-On-Chip: Optimizations and

Exploration