Phoenix: Detecting and Recovering from Permanent Processor Design Bugs with Programmable Hardware

> Smruti R. Sarangi Abhishek Tiwari Josep Torrellas

University of Illinois at Urbana-Champaign http://iacoma.cs.uiuc.edu

#### Can a Processor have a Design Defect ?

http://iacoma.cs.uiuc.edu

2

# A Major Challenge ???

50-70% effort spent on debugging

1-2 year verification times

Massive computational resources

# Defects slip through ???

- 1999 Defect leads to stoppage in shipping Pentium III servers

- 2004 AMD Opteron defect leads to data loss

- 2005 A version of Itanium 2 recalled

Does not look like it will stop

Increasing features on chip

Conventional approaches are ineffective

- Micro-code patching

- Compiler workarounds

- OS hacks

- Firmware

http://iacoma.cs.uiuc.edu

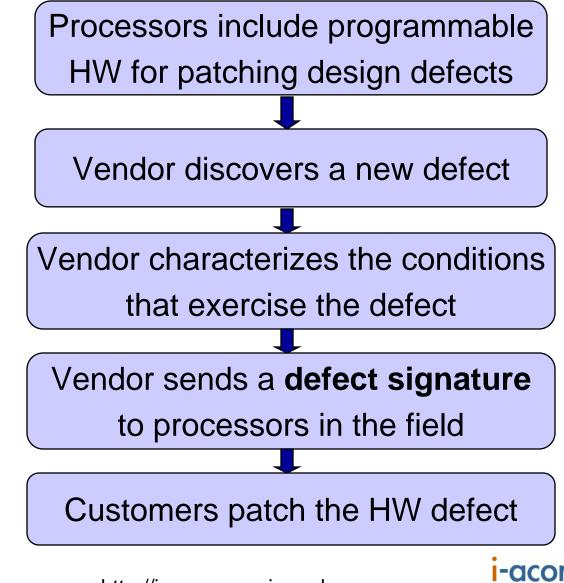

# Vision

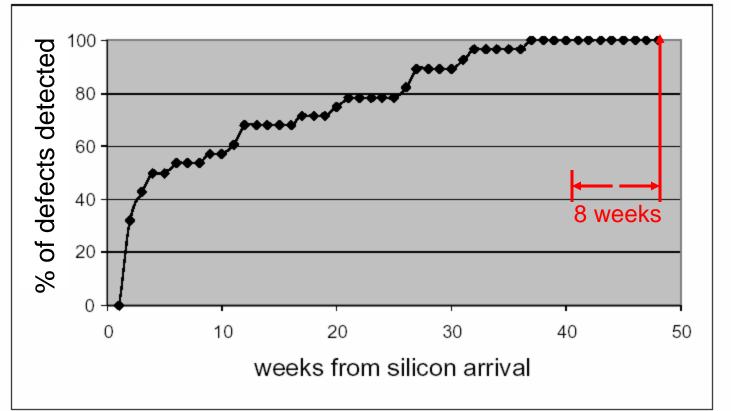

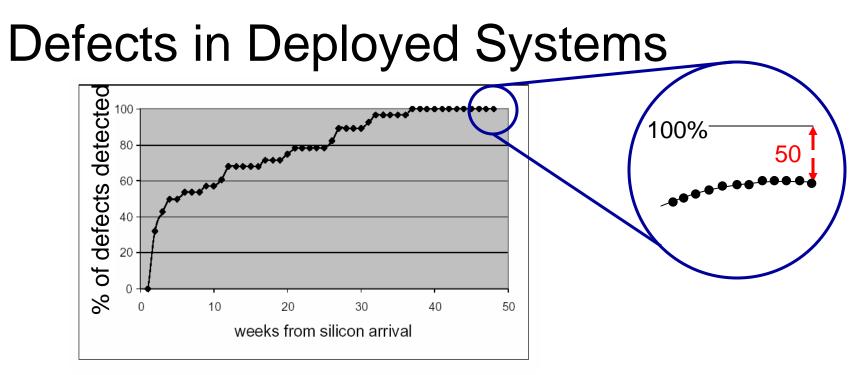

#### Additional Advantage: Reduced Time to Market

Pentium-M, Silas et al., 2003

Reduced time to market → Vital ingredient of profitability

# Outline

# Analysis and Characterization Architecture for Hardware Patching Evaluation

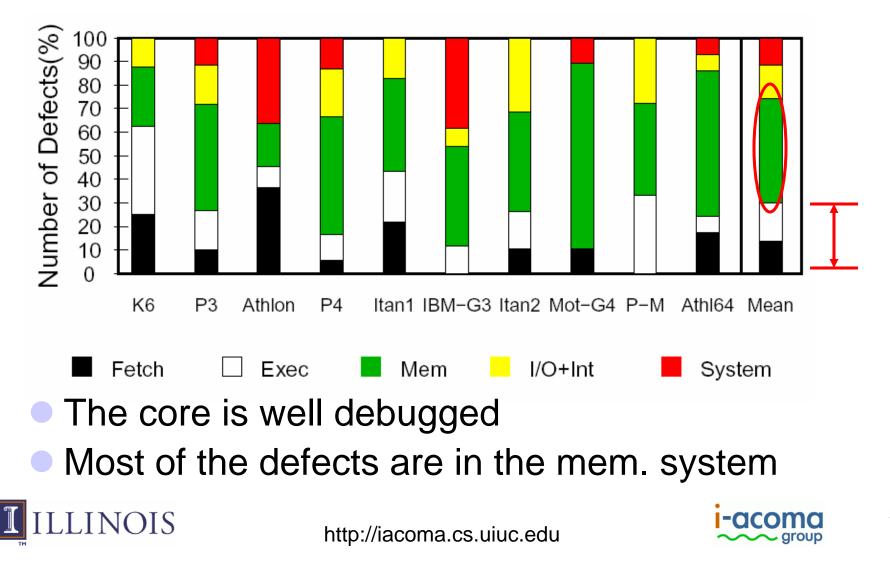

- We studied public domain errata documents for 10 current processors

- Intel Pentium III, IV, M, and Itanium I and II

- AMD K6, Athlon, Athlon 64

- IBM G3 (PPC 750 FX), MOT G4 (MPC 7457)

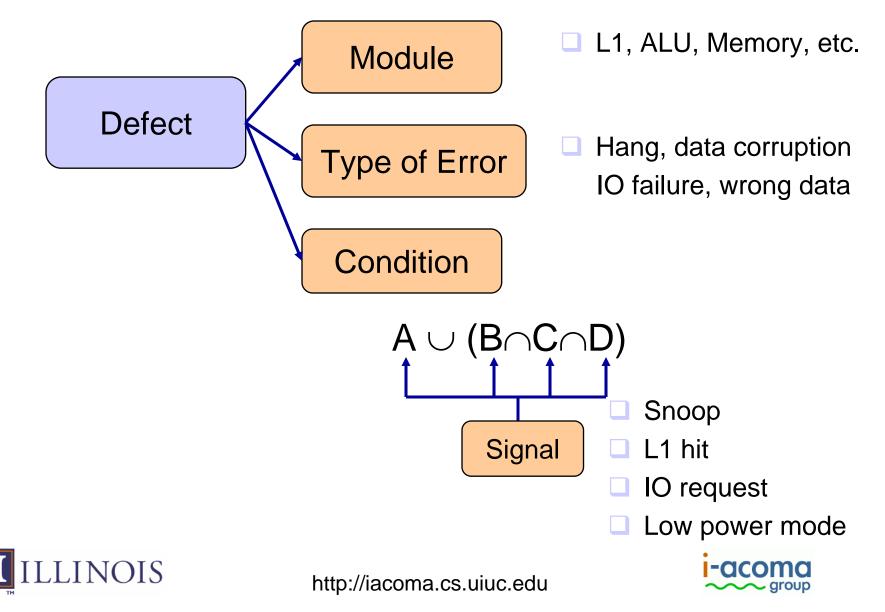

#### Dissecting a Defect – from Errata doc.

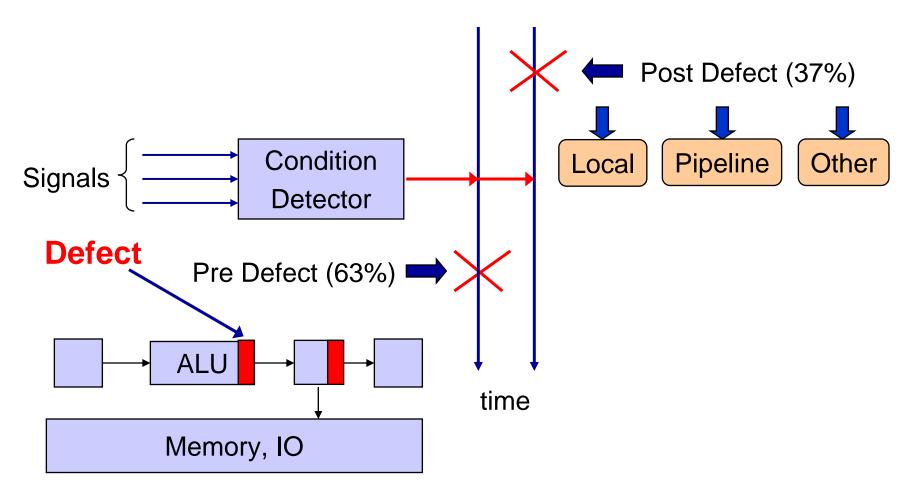

#### When can the defects be detected ?

# Outline

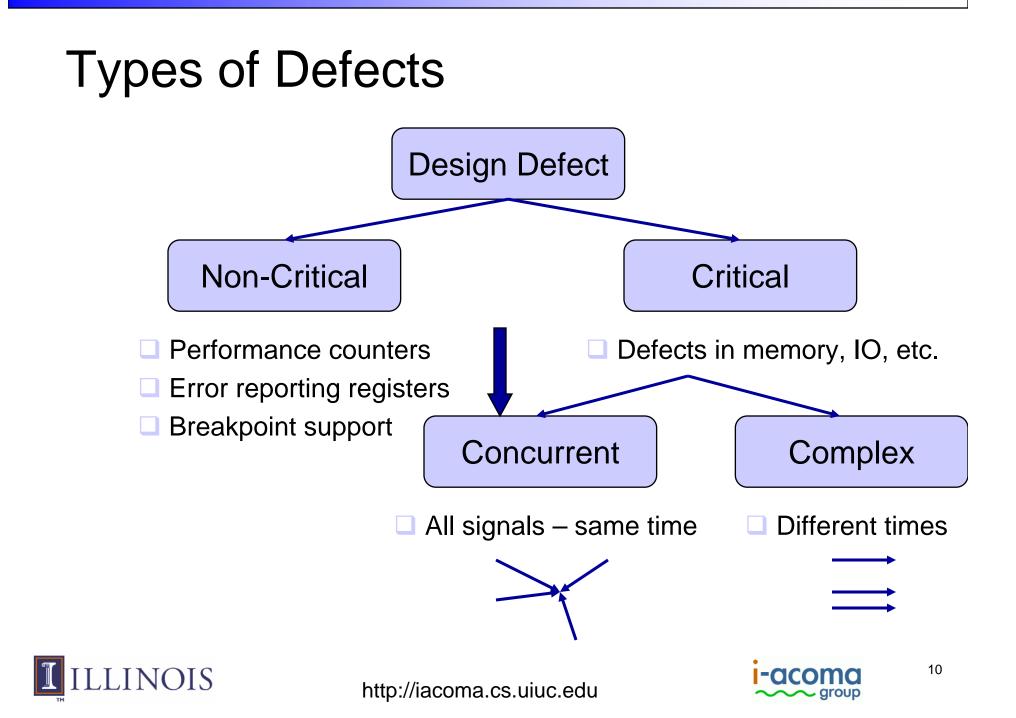

#### Analysis and Characterization

#### Architecture for Hardware Patching

#### Evaluation

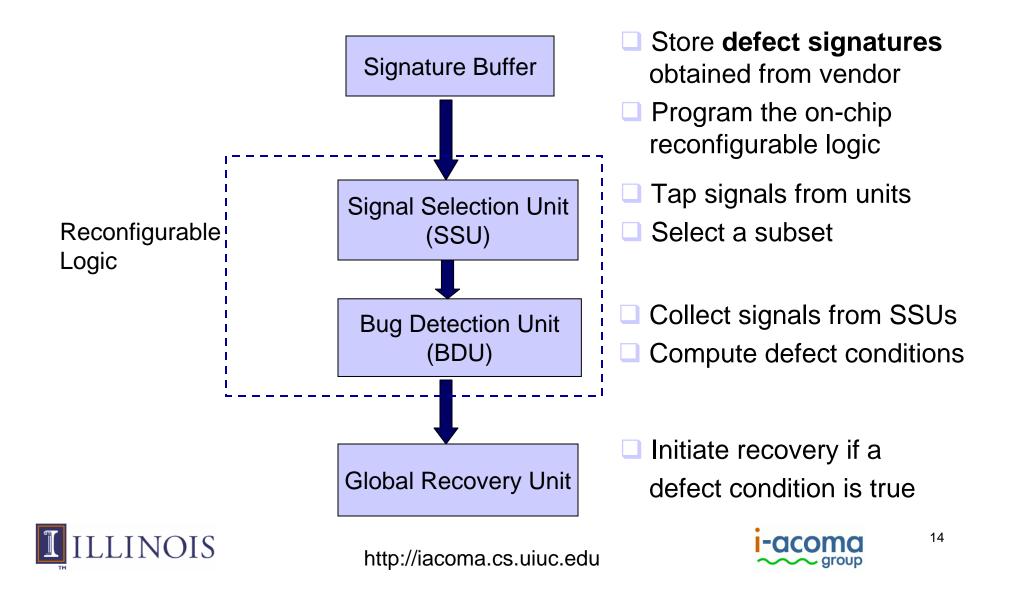

# Phoenix Conceptual Design

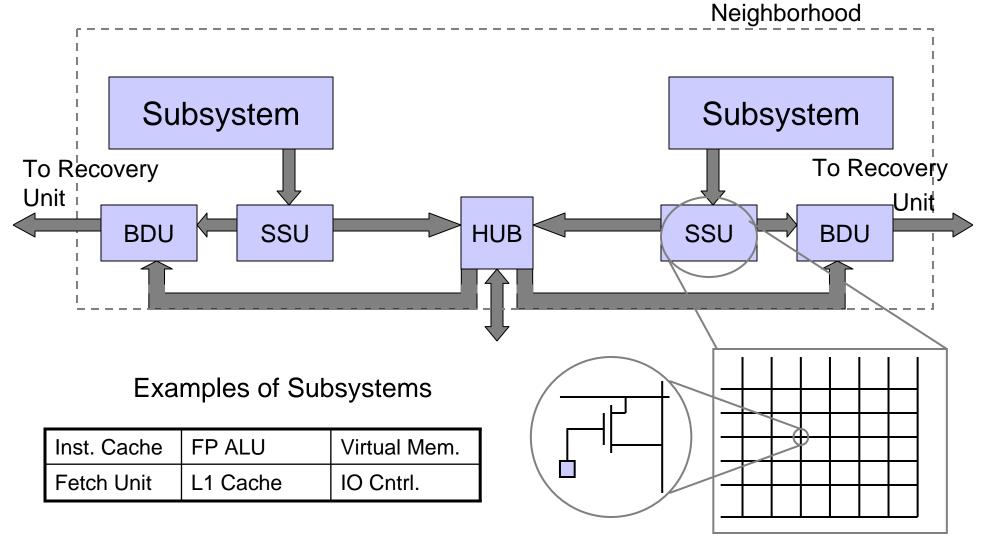

# Distributed Design of Phoenix

http://iacoma.cs.uiuc.edu

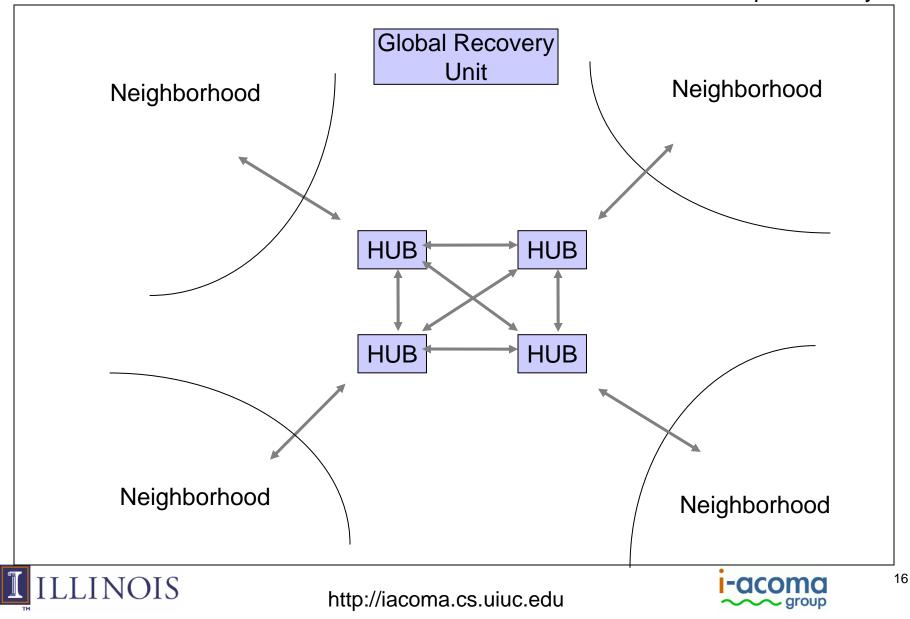

# **Overall Design**

Chip Boundary

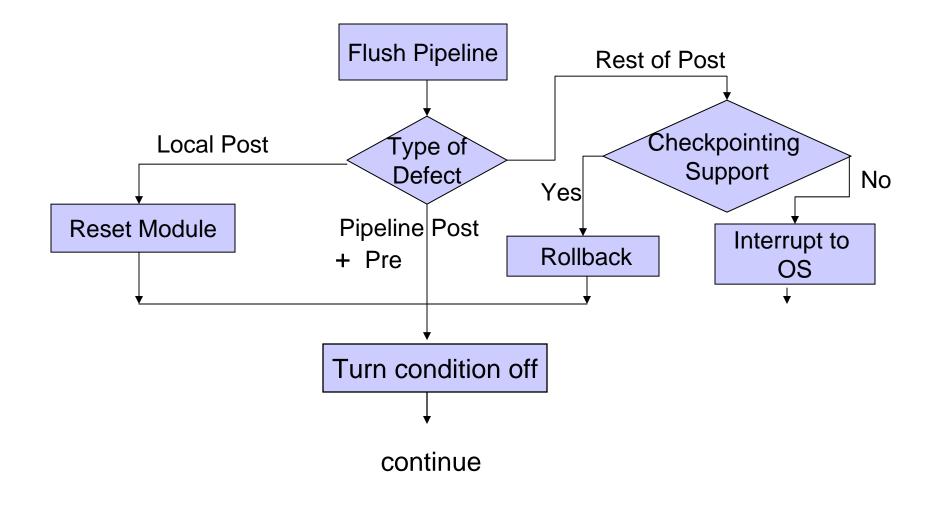

# Software Recovery Handler

17

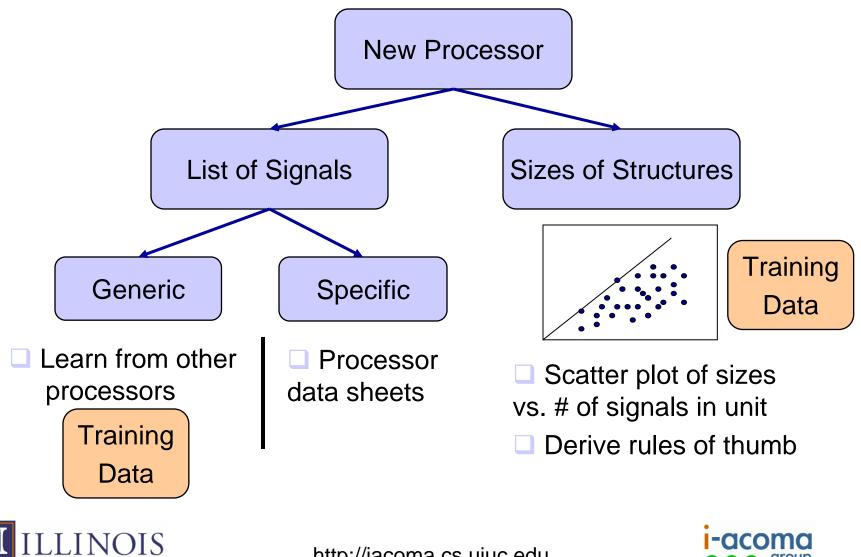

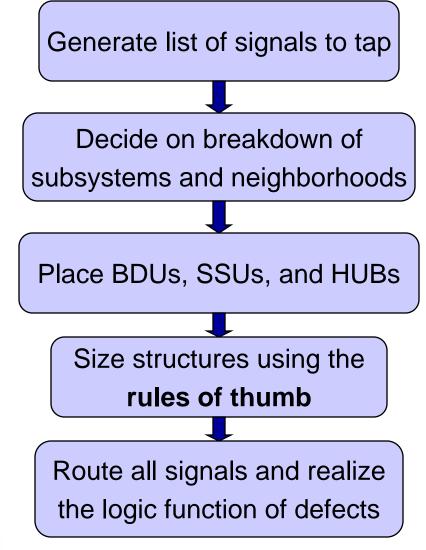

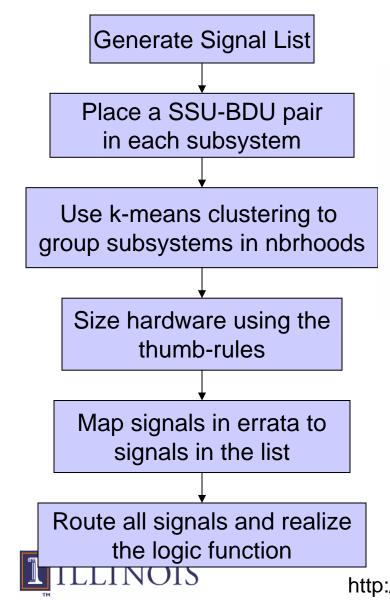

#### **Designing Phoenix for a New Processor**

#### Designing Phoenix for a New Proc. – II

http://iacoma.cs.uiuc.edu

# Outline

# Analysis and Characterization Architecture for Hardware Patching

#### Evaluation

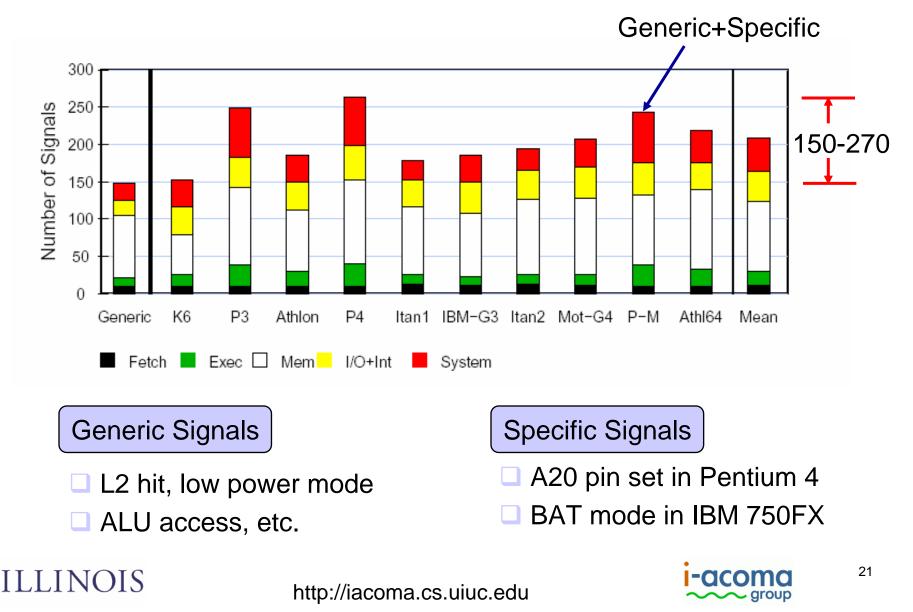

#### Signals Tapped

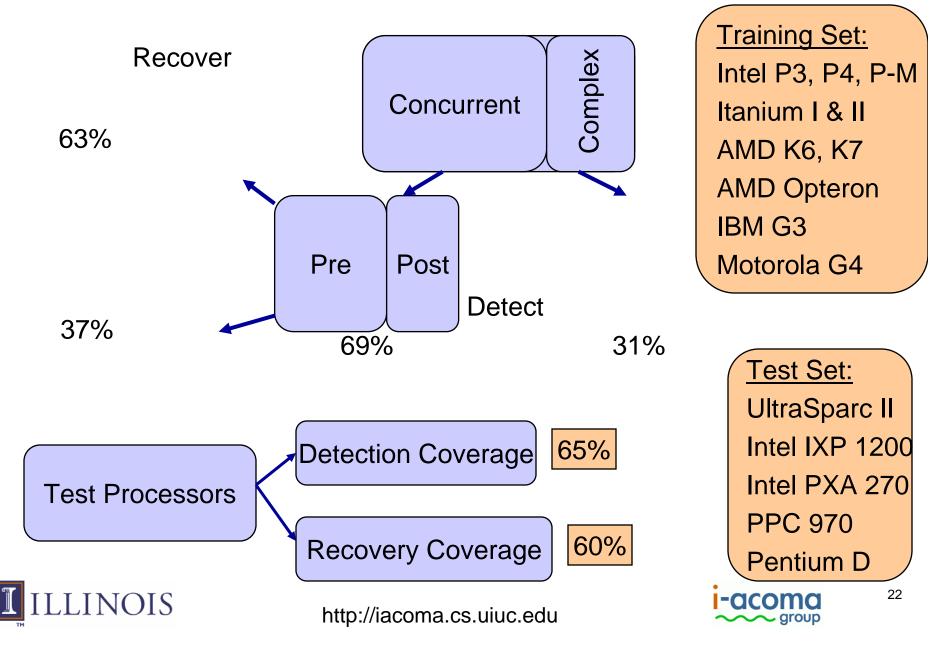

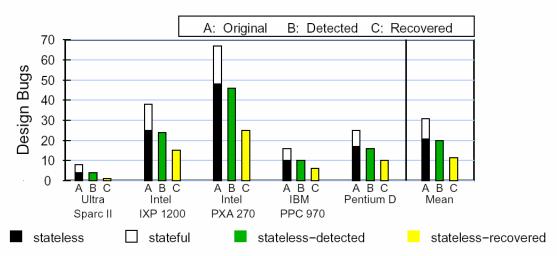

# **Defect Coverage Results**

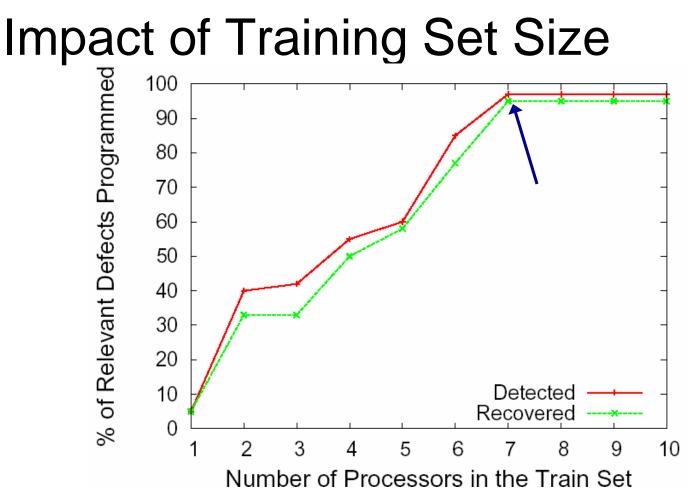

Train set only needs to have 7 processors

Coverage in new processors is very high

# Conclusion

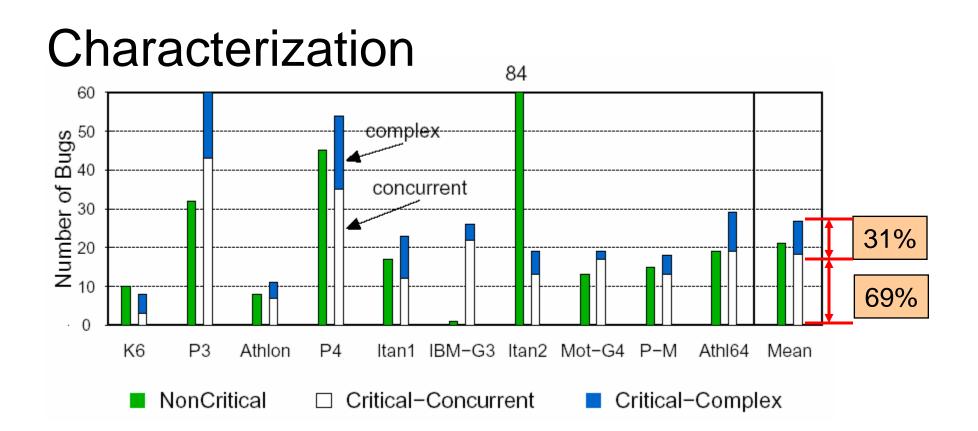

- We analyzed the defects in 10 processors

- Phoenix novel on-chip programmable HW

- Evaluated impact:

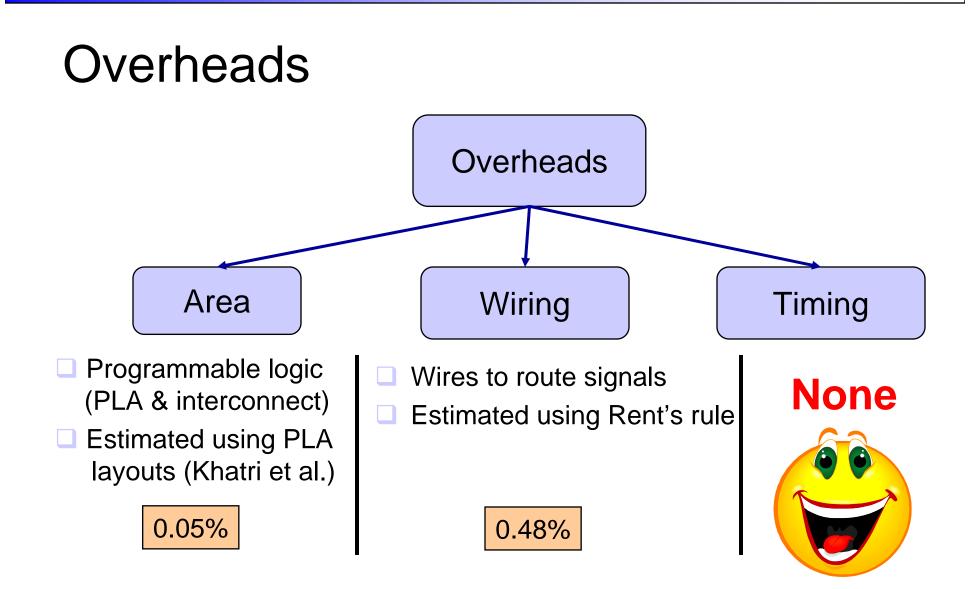

- 150 270 signals tapped

- Negligible area, wiring, and performance overhead

- Defect coverage: 69% detected, 63% recovered

- Algorithm to automatically size Phoenix for new procs

- We can now live with defects !!!

Phoenix: Detecting and Recovering from Permanent Processor Design Bugs with Programmable Hardware

> Smruti R. Sarangi Abhishek Tiwari Josep Torrellas

University of Illinois at Urbana-Champaign http://iacoma.cs.uiuc.edu

### Backup

http://iacoma.cs.uiuc.edu

27

#### Phoenix Algorithm for New Processors

Defect Coverage for New Processors

Similar results obtained for 9 Sun processors – UltraSparc III, III+, III++, IIIi, IIIe, IV, IV+, Niagara I and II

28

#### Where are the Critical defects ?